Записки CPU designer'a

RISC-V Summit North America 2023 Стартовал заключительный RISC-V Summit этого года. С 6 по 8 ноября запланированы выступления ведущих разработчиков в области экосистемы RISC-V. C расписанием докладов можно ознакомиться на сайте саммита. Из докладов конечно…

Стали доступны записи докладов с саммита RISC-V North America 2023 на YouTube 👀

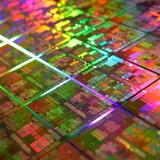

Принес вам ссылку на профиль с крутыми die shots.

У фотографа богатая коллекция снимков кристаллов процессоров от различных вендоров: AMD, Intel, Байкал, МЦСТ, Nvidia.

Например, вот ссылка на фотографии кристалла Baikal Electronics/BE-S1000 или фотографии кристалла gpu Nvidia/Pascal/GP106.

Больше siliconpr0n'a ищи по ссылке на фотохостинг 😎

#dieshots

У фотографа богатая коллекция снимков кристаллов процессоров от различных вендоров: AMD, Intel, Байкал, МЦСТ, Nvidia.

Например, вот ссылка на фотографии кристалла Baikal Electronics/BE-S1000 или фотографии кристалла gpu Nvidia/Pascal/GP106.

Больше siliconpr0n'a ищи по ссылке на фотохостинг 😎

#dieshots

Первые идеи для векторной спецификации RISC-V V 2.0

Одно из преимуществ открытой архитектуры это то что в live-режиме можно следить за технической дискуссией при выборе тех или иных решений и подходов при составлении архитектурной спецификации. Не так давно Qualcomm выступали с предложениями о пересмотре набора обязательных расширений для профиля RVA и подготовили ряд докладов о проблемах compressed расширения RISC-V.

Сегодня поговорим о предложениях (ключевое слово предложениях) одного из участников SIG: Vector Jose Moreira (Chair, IBM).

Одно из обсуждаемых решений в текущей имплементации векторной ISA - это конфигурационные инструкции, которые обновляют CSR. Эти инструкции находятся как бы на границе двух пайплайнов - векторного и системного (который отвечает за обновление конфигурации ядра) и имплементация данных инструкций нетривиальная задача. Однако, данные инструкции дают нативную поддержку stripmining vector. О примере имплементации таких инструкций писал в посте про RISC-V Ocelot.

Jose M. предлагает концепт Self-contained vector ISA, когда конфигурация вектора уже закодирована в самой инструкции. Но цена такого подхода - это расширение инструкции до 64-бит (либо до 48 бит), чтобы вместить те данные, которые в текущем подходе сохраняются в векторных CSR.

Какие плюсы можно выделить в этом подходе, по мнению автора канала:

1) повышение производительности за счет "высвобождения" системного пайплайна скалярного ядра;

2) простота отладки, т.к. каждая инструкция содержит конфигурацию вектора;

Минусы:

1) усложнение процесса извлечения инструкций - теперь нужно не только уметь извлекать и различать 16 битные инструкции и 32 битные, но и 64-битные;

2) усложнение логики branch predictor для корректного предсказания перехода с 3 типами длин инструкций;

3) усложнение логики скалярного декодера для различия compressed, non-compressed и 64-битных векторных инструкций;

4) если раньше скалярное ядро было драйвером VPU, то теперь обработка конфигурации вектора, определение запрещенных конфигураций будет обрабатываться внутри векторного конвейера;

Вместо заключения

Наличие 3 различных длин перегружает и усложняет fronted ядра фактически на всех этапах и делается в шаг, пусть и к размытой, нечеткой границе CISC подхода. Хотя задача изменения конфигурации вектора является важной, она не встречается достаточно часто в прикладных задачах, чтобы считать конфигурационные инструкции существенным bottleneck'ом в векторном расширении. Автору канала сложно понять мотивацию предложения нового формата векторного расширения, с акцентом на отказе от конфигурационных инструкций. Похоже, что в данном решении баланс между аппаратной поддержкой и бенефитами, которые оно предоставляет, не полностью продуман.

А в качестве вводной лекции про дизайн и микроархитектуру VPU предлагаю ознакомиться с презентацией от Tenstorrent.

К обсуждению приглашаю всех в комментарии к посту 🤓

Одно из преимуществ открытой архитектуры это то что в live-режиме можно следить за технической дискуссией при выборе тех или иных решений и подходов при составлении архитектурной спецификации. Не так давно Qualcomm выступали с предложениями о пересмотре набора обязательных расширений для профиля RVA и подготовили ряд докладов о проблемах compressed расширения RISC-V.

Сегодня поговорим о предложениях (ключевое слово предложениях) одного из участников SIG: Vector Jose Moreira (Chair, IBM).

Одно из обсуждаемых решений в текущей имплементации векторной ISA - это конфигурационные инструкции, которые обновляют CSR. Эти инструкции находятся как бы на границе двух пайплайнов - векторного и системного (который отвечает за обновление конфигурации ядра) и имплементация данных инструкций нетривиальная задача. Однако, данные инструкции дают нативную поддержку stripmining vector. О примере имплементации таких инструкций писал в посте про RISC-V Ocelot.

Jose M. предлагает концепт Self-contained vector ISA, когда конфигурация вектора уже закодирована в самой инструкции. Но цена такого подхода - это расширение инструкции до 64-бит (либо до 48 бит), чтобы вместить те данные, которые в текущем подходе сохраняются в векторных CSR.

Какие плюсы можно выделить в этом подходе, по мнению автора канала:

1) повышение производительности за счет "высвобождения" системного пайплайна скалярного ядра;

2) простота отладки, т.к. каждая инструкция содержит конфигурацию вектора;

Минусы:

1) усложнение процесса извлечения инструкций - теперь нужно не только уметь извлекать и различать 16 битные инструкции и 32 битные, но и 64-битные;

2) усложнение логики branch predictor для корректного предсказания перехода с 3 типами длин инструкций;

3) усложнение логики скалярного декодера для различия compressed, non-compressed и 64-битных векторных инструкций;

4) если раньше скалярное ядро было драйвером VPU, то теперь обработка конфигурации вектора, определение запрещенных конфигураций будет обрабатываться внутри векторного конвейера;

Вместо заключения

Наличие 3 различных длин перегружает и усложняет fronted ядра фактически на всех этапах и делается в шаг, пусть и к размытой, нечеткой границе CISC подхода. Хотя задача изменения конфигурации вектора является важной, она не встречается достаточно часто в прикладных задачах, чтобы считать конфигурационные инструкции существенным bottleneck'ом в векторном расширении. Автору канала сложно понять мотивацию предложения нового формата векторного расширения, с акцентом на отказе от конфигурационных инструкций. Похоже, что в данном решении баланс между аппаратной поддержкой и бенефитами, которые оно предоставляет, не полностью продуман.

А в качестве вводной лекции про дизайн и микроархитектуру VPU предлагаю ознакомиться с презентацией от Tenstorrent.

К обсуждению приглашаю всех в комментарии к посту 🤓

GitHub

vector/minutes/2023/2023-11-20 at main · riscv-admin/vector

Group administration repository for SIG: Vector. Contribute to riscv-admin/vector development by creating an account on GitHub.

Сегодня хочу поделиться с вами ссылками на must see материалы, которые я нашел на этой неделе 🤓

1. Пост Юрия Панчула на сайте Истового Инженера - ASIC и FPGA: сорок лет эволюции. Крутой ликбез для понимания что же такое дизайн цифровых схем, при помощи каких инструментов проектируются современные ASIC, зачем нужен MPW и чем хороши FPGA в обучении студентов.

2. Канал Сергея Чусова про верификацию цифровых устройств. Сергея вы можете знать по его лекциям в Школе Синтеза Цифровых Схем.

Рекомендую к просмотру лекцию [ссылка с таймкодом] Сергея про Теорию SystemVerilog Assertions.

1. Пост Юрия Панчула на сайте Истового Инженера - ASIC и FPGA: сорок лет эволюции. Крутой ликбез для понимания что же такое дизайн цифровых схем, при помощи каких инструментов проектируются современные ASIC, зачем нужен MPW и чем хороши FPGA в обучении студентов.

2. Канал Сергея Чусова про верификацию цифровых устройств. Сергея вы можете знать по его лекциям в Школе Синтеза Цифровых Схем.

Рекомендую к просмотру лекцию [ссылка с таймкодом] Сергея про Теорию SystemVerilog Assertions.

Истовый инженер

ASIC и FPGA: сорок лет эволюции

Внутри каждого современного телефона несколько микросхем ASIC. Ими наполнены автомобили, стойки в центрах обработки данных, датчики «умного дома», и вообще все электронные устройства. Без чипов ASIC был бы невозможен быстрый интернет, трехмерные игры и ускорители…

Сегодня принес ссылку на must see доклад Школы Синтеза Цифровых Схем - Инженерные диаграммы WaveDrom

Доклад читает автор программы для инженерных диаграмм WaveDrom, Staff Engineer в компании SiFive (одного из лидеров и основных драйверов RISC-V сообщества) — Алексей Чепыженко.

WaveDrom диаграммы сейчас являются одним из основных инструментов для документирования поведения аппаратных блоков.

Все полупроводниковые компании, в которых автор канала успел поработать, в той или иной степени использовали WaveDrom для составления внутренней и пользовательской документации.

Hardware community также внедрило инструмент поддержки рендера временных диаграмм для VS Code, например TerosHDL или Waveform Render. С помощью данных расширений вы можете использовать псевдокод для создания временных диаграмм и вставлять их непосредственно в комментарии к исходным файлам, повышая документированность кода.

В заключение, доклад Алексея Чепыженко о инженерных диаграммах WaveDrom представляет собой обязательный источник знаний для всех, кто занимается проектированием, верификацией и документированием аппаратных блоков. WaveDrom не только облегчает процесс создания временных диаграмм, но и улучшает читаемость и понимание поведения аппаратных компонентов.

p.s. и не каждый день ведущий инженер из SiFive читает доклад в Школе Синтеза, такое пропускать точно не стоит 😎

Доклад читает автор программы для инженерных диаграмм WaveDrom, Staff Engineer в компании SiFive (одного из лидеров и основных драйверов RISC-V сообщества) — Алексей Чепыженко.

WaveDrom диаграммы сейчас являются одним из основных инструментов для документирования поведения аппаратных блоков.

Все полупроводниковые компании, в которых автор канала успел поработать, в той или иной степени использовали WaveDrom для составления внутренней и пользовательской документации.

Hardware community также внедрило инструмент поддержки рендера временных диаграмм для VS Code, например TerosHDL или Waveform Render. С помощью данных расширений вы можете использовать псевдокод для создания временных диаграмм и вставлять их непосредственно в комментарии к исходным файлам, повышая документированность кода.

В заключение, доклад Алексея Чепыженко о инженерных диаграммах WaveDrom представляет собой обязательный источник знаний для всех, кто занимается проектированием, верификацией и документированием аппаратных блоков. WaveDrom не только облегчает процесс создания временных диаграмм, но и улучшает читаемость и понимание поведения аппаратных компонентов.

p.s. и не каждый день ведущий инженер из SiFive читает доклад в Школе Синтеза, такое пропускать точно не стоит 😎

C наступившим новым годом! 😄

Принес вам статистику канала за прошлый год. Значительно увеличилось число просмотров и подписчиков, что, конечно же, не может не радовать автора канала.

Своим трудом, как автор, за прошедший год остался доволен, ну почти.

Спасибо вам, что читаете, делитесь, активно участвуете в обсуждении в комментариях. Особенно радует то, что вокруг канала формируется комьюнити энтузиастов, которые разделяют интерес к проектированию процессоров и цифровому синтезу. Дальше - больше.

Желаю вам, чтобы в новом году тайминги сходились, программы из прерываний выходили, чтобы промахов в кэшах не было, а NaN'ы в ответах не попадались.

Stay tuned😉

Принес вам статистику канала за прошлый год. Значительно увеличилось число просмотров и подписчиков, что, конечно же, не может не радовать автора канала.

Своим трудом, как автор, за прошедший год остался доволен, ну почти.

Спасибо вам, что читаете, делитесь, активно участвуете в обсуждении в комментариях. Особенно радует то, что вокруг канала формируется комьюнити энтузиастов, которые разделяют интерес к проектированию процессоров и цифровому синтезу. Дальше - больше.

Желаю вам, чтобы в новом году тайминги сходились, программы из прерываний выходили, чтобы промахов в кэшах не было, а NaN'ы в ответах не попадались.

Stay tuned

Please open Telegram to view this post

VIEW IN TELEGRAM

SiFive выложила в общий доступ часть документации для собственной имплементации Matrix Multiplication Extensions.

Эти материалы доступны по следующим ссылкам:

SiFive MatMul Extension for integer

SiFive MatMul Extension for bfloat

Это может быть первыми шагами в направлении популяризации собственной ISA (Instruction Set Architecture) для новой спецификации Integrated Matrix Extensions (IME).

Свое видение для Matrix Multiplication уже представляла компания T-HEAD на Китайском RISC-V саммите. С презентацией T-HEAD о матричном расширение можно ознакомиться по ссылке.

На Североамериканском саммите о реализации матричных умножителей также заявили компании Semidynamics и Andes Techology. По ссылкам выше вы можете ознакомиться с докладами этих компаний.

Напоминаю, что за ходом работы разработки нового матричного расширения можно следить на github

Эти материалы доступны по следующим ссылкам:

SiFive MatMul Extension for integer

SiFive MatMul Extension for bfloat

Это может быть первыми шагами в направлении популяризации собственной ISA (Instruction Set Architecture) для новой спецификации Integrated Matrix Extensions (IME).

Свое видение для Matrix Multiplication уже представляла компания T-HEAD на Китайском RISC-V саммите. С презентацией T-HEAD о матричном расширение можно ознакомиться по ссылке.

На Североамериканском саммите о реализации матричных умножителей также заявили компании Semidynamics и Andes Techology. По ссылкам выше вы можете ознакомиться с докладами этих компаний.

Напоминаю, что за ходом работы разработки нового матричного расширения можно следить на github

SiFive

SiFive Documentation

Manuals, user guides, and other documentation for SiFive's RISC-V Core IP, chips, development boards, and tools.

Вышло обновление лучшего курса по работе с RISC-V ядром - RVfpga 3.0

Из новинок в курсе можно выделить основные изменения:

1) Поддержка Catapult SDK от Imagination (только VeeR EL2), автор канала настоятельно рекомендует продолжать пользоваться PlatformIO для получения большего набора компетенций и навыков.

2) Была добавлена предварительно настроенная виртуальная машина на базе Ubuntu с установленным всем необходимым программным обеспечением. Это существенно облегчает начало работы с учебным материалом.

3) Добавлена поддержка ядра VeeR EL2, меньшего по размеру ядра в сравнении с оригинальным ядром курса - VeeR EH1. Данное изменение позволит адаптировать под курс больше отладочных плат с менее мощными и дешевыми FPGA на борту.

4) Добавлены инструменты симуляции RVfpga-ViDBo and RVfpga-Pipeline. Их исходники можно найти в курсе и изучить возможность адаптации простейших тулов ко-симуляции для ваших личных задач и нужд.

Для того чтобы получить доступ к курсу необходимо заполнить специальную форму академического доступа. В течении 1-3 рабочих дней вам должны предоставить ссылку для скачивания материалов.

Из новинок в курсе можно выделить основные изменения:

1) Поддержка Catapult SDK от Imagination (только VeeR EL2), автор канала настоятельно рекомендует продолжать пользоваться PlatformIO для получения большего набора компетенций и навыков.

2) Была добавлена предварительно настроенная виртуальная машина на базе Ubuntu с установленным всем необходимым программным обеспечением. Это существенно облегчает начало работы с учебным материалом.

3) Добавлена поддержка ядра VeeR EL2, меньшего по размеру ядра в сравнении с оригинальным ядром курса - VeeR EH1. Данное изменение позволит адаптировать под курс больше отладочных плат с менее мощными и дешевыми FPGA на борту.

4) Добавлены инструменты симуляции RVfpga-ViDBo and RVfpga-Pipeline. Их исходники можно найти в курсе и изучить возможность адаптации простейших тулов ко-симуляции для ваших личных задач и нужд.

Для того чтобы получить доступ к курсу необходимо заполнить специальную форму академического доступа. В течении 1-3 рабочих дней вам должны предоставить ссылку для скачивания материалов.

Spartan 3 - good night sweet prince

Автор канала был уверен, что Spartan-3 и прочих старичков линеек Xilinx сняли уже с производства лет 5 назад, но незаметный Discontinuation Notice от AMD оповестил, что только в этом году прекращается производства семейств XC9500XL, CoolRunner XPLA 3, CoolRunner II, Spartan II, а также Spartan 3, 3A, 3AN, 3E, 3ADSP.

Spartan-3 оставил свой след в истории как одна из первых доступных на рынке серий ПЛИС, использующих технологический процесс с нормой 90 нанометров.

Если по каким-либо причинам в качестве целевого вычислительного ядра в вашем проекте вы используете вышеупомянутые модели, то крайний срок для совершения заказов на устройства 29 июня 2024 года.

А вообще, господа, пора задуматься о переходе на Spartan-6😂

Автор канала был уверен, что Spartan-3 и прочих старичков линеек Xilinx сняли уже с производства лет 5 назад, но незаметный Discontinuation Notice от AMD оповестил, что только в этом году прекращается производства семейств XC9500XL, CoolRunner XPLA 3, CoolRunner II, Spartan II, а также Spartan 3, 3A, 3AN, 3E, 3ADSP.

Spartan-3 оставил свой след в истории как одна из первых доступных на рынке серий ПЛИС, использующих технологический процесс с нормой 90 нанометров.

Если по каким-либо причинам в качестве целевого вычислительного ядра в вашем проекте вы используете вышеупомянутые модели, то крайний срок для совершения заказов на устройства 29 июня 2024 года.

А вообще, господа, пора задуматься о переходе на Spartan-6

Please open Telegram to view this post

VIEW IN TELEGRAM

TechPowerUp

AMD Discontinues Selection of Old Xilinx CPLD & FPGA Models

AMD has quietly issued a product discontinuation notice—their PDF document is dated January 1 2024—for a whole bunch of Xilinx Complex Programmable Logic Device (CLPD) and lower-end FPGA models. Team Red's opening statement on the matter reads: "AMD will…

Зимняя школа Программирование для RISC-V 2-8 февраля 2024 года

Всем привет, сегодня принес анонс открытого и бесплатного интенсива от компании YADRO и Университета Лобачевского.

В школе будут представлены лекции о компьютерной архитектуре, наборе команд RISC-V, а также с особенностям векторного расширения. На занятиях открытой зимней школы вы так же освоите методы повышения производительности и оптимизации ПО.

Регистрация открыта и доступна для всех онлайн, однако проектная работа пройдет очно в Нижнем Новгороде.

Успеть зарегистрироваться нужно до 29 января, а тем кто хочет прийти очно на трек по проектной работе — нужно пройти отбор из-за ограниченного количества мест.

Для доступа к прослушиванию лекций на трансляции нужна предварительная регистрация. Обратите внимание, что письмо-подтверждение после регистрации может улететь в спам, не забудьте проверить.

Всем привет, сегодня принес анонс открытого и бесплатного интенсива от компании YADRO и Университета Лобачевского.

В школе будут представлены лекции о компьютерной архитектуре, наборе команд RISC-V, а также с особенностям векторного расширения. На занятиях открытой зимней школы вы так же освоите методы повышения производительности и оптимизации ПО.

Регистрация открыта и доступна для всех онлайн, однако проектная работа пройдет очно в Нижнем Новгороде.

Успеть зарегистрироваться нужно до 29 января, а тем кто хочет прийти очно на трек по проектной работе — нужно пройти отбор из-за ограниченного количества мест.

Для доступа к прослушиванию лекций на трансляции нужна предварительная регистрация. Обратите внимание, что письмо-подтверждение после регистрации может улететь в спам, не забудьте проверить.

В продаже появилась отладочная плата на база ядра C908 c поддержкой векторного расширения RVV 1.0

Эта базовая отладочная плата предназначена для проведения бенчмарков и тестов на реальном оборудовании с поддержкой RVV 1.0. Процессор на плате выполнен в двухъядерной конфигурации: одно ядро энергоэффективное, а второе — высокопроизводительное с поддержкой векторного сопроцессора.

Сказать, что ядро подходит для general AI-computing нельзя, но для малых ускорителей уже придуман новый термин — AIoT, на нем и остановимся.

Ядро с поддержкой векторного сопроцессора работает на частоте 1.6 GHz, VLEN определена разрядностью в 128 бит, что эквивалентно 4 32-битным элементам или 8 16-битным элементам в векторе. Чип K230, помимо VPU, содержит AI Subsystems с поддержкой типов данных INT8/16. Значения бенчмарков для типичных нейросетей и список аппаратно поддерживаемых функций найдете в документации на процессор.

Полезные ссылки:

1) Документация на отладочную плату CanMV-K230.

2) Документация на ядро C908 на сайте XuanTie.

3) Документация на чип K230.

Эта базовая отладочная плата предназначена для проведения бенчмарков и тестов на реальном оборудовании с поддержкой RVV 1.0. Процессор на плате выполнен в двухъядерной конфигурации: одно ядро энергоэффективное, а второе — высокопроизводительное с поддержкой векторного сопроцессора.

Сказать, что ядро подходит для general AI-computing нельзя, но для малых ускорителей уже придуман новый термин — AIoT, на нем и остановимся.

Ядро с поддержкой векторного сопроцессора работает на частоте 1.6 GHz, VLEN определена разрядностью в 128 бит, что эквивалентно 4 32-битным элементам или 8 16-битным элементам в векторе. Чип K230, помимо VPU, содержит AI Subsystems с поддержкой типов данных INT8/16. Значения бенчмарков для типичных нейросетей и список аппаратно поддерживаемых функций найдете в документации на процессор.

Полезные ссылки:

1) Документация на отладочную плату CanMV-K230.

2) Документация на ядро C908 на сайте XuanTie.

3) Документация на чип K230.

Бесплатная конференция по маршруту верификации и прототипирования Систем на Кристалле от инженеров Yadro

Делюсь с вами ссылкой на открытый хардверный митап.

Со списком докладов вы можете ознакомиться на сайте митапа.

Особое внимание хочется обратить на доклад Анатолия Лернера "Имплементация больших дизайнов на FPGA-кластерах". Прототипирование IP-блоков на реальном оборудовании является актуальной задачей любой компании, которая занимается дизайном в сфере микроэлектроники. Размещение целевого дизайна на FPGA-плате превращается из рутинной задачи в сложную инженерную проблему, когда дизайн распределяется по 2, 3 или даже 8 кристаллам FPGA. Это влечет за собой необходимость в разработке методов распределения частей дизайна по различным физическим чипам, создании систем обмена данными между отладочными платами и чипами, а иногда и разработке единой материнской платы для всего кластера.

Представители большой тройки EDA так же представляют услуги по прототипированию дизайна на FPGA-кластерах.

Например один из продуктов ведущего разработчика EDA, Synospsys - это продажа специальной платформы прототипирования HAPS.

Siemens, не так давно приобрела компанию proFPGA, которая специализируется на проектировании FPGA-кластеров для задач прототипирования.

Интересно, как подошли к решению этой задачи инженеры из команды Yadro.

Для участия в офлайн или онлайн части конференции нужно пройти предварительную регистрацию на сайте ивента.

Делюсь с вами ссылкой на открытый хардверный митап.

Со списком докладов вы можете ознакомиться на сайте митапа.

Особое внимание хочется обратить на доклад Анатолия Лернера "Имплементация больших дизайнов на FPGA-кластерах". Прототипирование IP-блоков на реальном оборудовании является актуальной задачей любой компании, которая занимается дизайном в сфере микроэлектроники. Размещение целевого дизайна на FPGA-плате превращается из рутинной задачи в сложную инженерную проблему, когда дизайн распределяется по 2, 3 или даже 8 кристаллам FPGA. Это влечет за собой необходимость в разработке методов распределения частей дизайна по различным физическим чипам, создании систем обмена данными между отладочными платами и чипами, а иногда и разработке единой материнской платы для всего кластера.

Представители большой тройки EDA так же представляют услуги по прототипированию дизайна на FPGA-кластерах.

Например один из продуктов ведущего разработчика EDA, Synospsys - это продажа специальной платформы прототипирования HAPS.

Siemens, не так давно приобрела компанию proFPGA, которая специализируется на проектировании FPGA-кластеров для задач прототипирования.

Интересно, как подошли к решению этой задачи инженеры из команды Yadro.

Для участия в офлайн или онлайн части конференции нужно пройти предварительную регистрацию на сайте ивента.

Surfer Project

Сегодня принес вам opensource проект waveform viewer'a Surfer.

Одной из фишек проекта является его возможность запуска в различных операционных системах: Windows, Linux, а также в веб-браузере.

Для запуска demo-примера в браузере нажмите на гиперссылку на 4-й строчки описания проекта.

Список реализованных и находящихся в разработке функций можно найти на GitLab'e проекта.

Из крутых особенностей стоит отметить поддержку декодирования 8-битных чисел с плавающей запятой: E5M2, E4M3. Также замечен тип данных Posit с поддержкой Quire.

Команда проекта также имеет планы по декодированию инструкций RISC-V. На данный момент реализована поддержка набора RV32I. А так же поддержка для пользовательских декодеров, для кастомных типов данных.

Для чтения дампов поддерживаются типы данных VCD и FST.

Кроме того, разработчики заявляют о интеграции новой библиотеки для чтения дампов большого объёма. Например, один из авторов утверждает, что удалось добиться чтения VCD объёмом в 7 Гб за 6 секунд, что является впечатляющим результатом.

Узнать о проекте больше, сообщить об ошибках или присоединиться к разработке можно на GitLab'е проекта.

А если хотите получше узнать разработчиков проекта, их идею и мотивацию, то в блоге YosysHQ есть классное интервью с разработчиками Surfer.

Сегодня принес вам opensource проект waveform viewer'a Surfer.

Одной из фишек проекта является его возможность запуска в различных операционных системах: Windows, Linux, а также в веб-браузере.

Для запуска demo-примера в браузере нажмите на гиперссылку на 4-й строчки описания проекта.

Список реализованных и находящихся в разработке функций можно найти на GitLab'e проекта.

Из крутых особенностей стоит отметить поддержку декодирования 8-битных чисел с плавающей запятой: E5M2, E4M3. Также замечен тип данных Posit с поддержкой Quire.

Команда проекта также имеет планы по декодированию инструкций RISC-V. На данный момент реализована поддержка набора RV32I. А так же поддержка для пользовательских декодеров, для кастомных типов данных.

Для чтения дампов поддерживаются типы данных VCD и FST.

Кроме того, разработчики заявляют о интеграции новой библиотеки для чтения дампов большого объёма. Например, один из авторов утверждает, что удалось добиться чтения VCD объёмом в 7 Гб за 6 секунд, что является впечатляющим результатом.

Узнать о проекте больше, сообщить об ошибках или присоединиться к разработке можно на GitLab'е проекта.

А если хотите получше узнать разработчиков проекта, их идею и мотивацию, то в блоге YosysHQ есть классное интервью с разработчиками Surfer.

Please open Telegram to view this post

VIEW IN TELEGRAM

Бесплатный курс по Верификации систем на кристалле от компании YADRO.

Принес вам еще один бесплатный курс.

На курсе инженеры из компании Ядро расскажут вам о процессе проектирования систем на кристалле (СнК) и о том, как верификация играет важную роль в этом процессе.

На курсе вы узнаете о функциональной и формальной верификации, их назначении и применении. Познакомитесь с новомодным фреймворком cocotb, изучите инструменты ко-симуляции, попрактикуетесь в работе с несинтезируемом подмножеством SystemVerilog.

Курс длится около 2.5 месяцев, посещение занятий возможно как онлайн, так и офлайн в офисе YADRO.

Прием заявок открыт до 17 марта включительно. В анкете не забудь выбрать интересующий тебя курс.

Обучение на курсе бесплатное, а лучших участников пригласят на стажировку в YADRO.

GLHF☕️

Принес вам еще один бесплатный курс.

На курсе инженеры из компании Ядро расскажут вам о процессе проектирования систем на кристалле (СнК) и о том, как верификация играет важную роль в этом процессе.

На курсе вы узнаете о функциональной и формальной верификации, их назначении и применении. Познакомитесь с новомодным фреймворком cocotb, изучите инструменты ко-симуляции, попрактикуетесь в работе с несинтезируемом подмножеством SystemVerilog.

Курс длится около 2.5 месяцев, посещение занятий возможно как онлайн, так и офлайн в офисе YADRO.

Прием заявок открыт до 17 марта включительно. В анкете не забудь выбрать интересующий тебя курс.

Обучение на курсе бесплатное, а лучших участников пригласят на стажировку в YADRO.

GLHF

Please open Telegram to view this post

VIEW IN TELEGRAM

Сегодня принес вам крепкий лонгрид про открытое образование☺️

Давно у меня была идея сделать пост про открытые курсы в области процессорных архитектур и цифрового дизайна.

Но формат из склеенных постов в телеграмме или оформление в телеграфе, как я делал с прошлогодним лонгридом про EPI, мне не совсем заходят.

В коллабе с Истовым Инженером подготовили для вас две статьи.

1. Разработка микросхем: первое знакомство с инженерными специальностями и инструментами.

Это вводная статья подойдет для тех, кто только начинает интересоваться миром цифрового дизайна. По большей части статья является подводкой к материалу про открытое образование, чтобы читатель имел понимание чему и зачем он будет обучаться. В статье поговорили, кто же такие RTL-дизайнеры, верификаторы, топологи, что такое и зачем нужны архитектурные лицензии, а так же где работают инженеры по разработке аппаратного обеспечения.

2. Где учиться разработке микропроцессоров: подборка бесплатных курсов ведущих вузов.

Тот самый прекрасный лонгрид из заголовка. Здесь собраны наиболее актуальные и полезные инструменты и ресурсы для погружения в мир Компьютерных Архитектур и Цифрового Дизайна, по моему скромномуи единственно верному мнению. Все как мы любимым, красивая верстка и картинки, на все курсы приведены актуальные ссылки. Все курсы бесплатные, условия доступа к материалам по каждому из курса описаны в статье.

Вместо заключения

Хотелось бы выразить благодарность редакторскому составу Истового Инженера, без чьего вклада эти статьи не увидели бы свет. Особая признательность Анне Лесных и Ульяне Малышевой за их помощь в создании и редактировании материалов.

Stay Tuned 😎

#лонгрид

Давно у меня была идея сделать пост про открытые курсы в области процессорных архитектур и цифрового дизайна.

Но формат из склеенных постов в телеграмме или оформление в телеграфе, как я делал с прошлогодним лонгридом про EPI, мне не совсем заходят.

В коллабе с Истовым Инженером подготовили для вас две статьи.

1. Разработка микросхем: первое знакомство с инженерными специальностями и инструментами.

Это вводная статья подойдет для тех, кто только начинает интересоваться миром цифрового дизайна. По большей части статья является подводкой к материалу про открытое образование, чтобы читатель имел понимание чему и зачем он будет обучаться. В статье поговорили, кто же такие RTL-дизайнеры, верификаторы, топологи, что такое и зачем нужны архитектурные лицензии, а так же где работают инженеры по разработке аппаратного обеспечения.

2. Где учиться разработке микропроцессоров: подборка бесплатных курсов ведущих вузов.

Тот самый прекрасный лонгрид из заголовка. Здесь собраны наиболее актуальные и полезные инструменты и ресурсы для погружения в мир Компьютерных Архитектур и Цифрового Дизайна, по моему скромному

Вместо заключения

Хотелось бы выразить благодарность редакторскому составу Истового Инженера, без чьего вклада эти статьи не увидели бы свет. Особая признательность Анне Лесных и Ульяне Малышевой за их помощь в создании и редактировании материалов.

Stay Tuned 😎

#лонгрид

Please open Telegram to view this post

VIEW IN TELEGRAM

ESP the open-source SoC platform

ESP - это открытая платформа для проектирования и создания гетерогенных System on a chip c возможностью прототипирования системы на FPGA. В будущем планируется также поддержка ASIC design flow.

ESP предоставляет гибкую tile-based архитектуру, построенную на multi-plane network-on-chip

Обзор проекта представлен авторами в статье Agile SoC Development with Open ESP.

В проекте вы найдете знакомые многим RISC-V энтузиастам названия открытых процессорных IP: Ariane (CVA6), ibex, LEON3 (на базе SPARC V8 32-bits ISA). Но самые внимательные увидят на изображении floorplan'а чипа в заголовке поста NVDLA —opensource Deep Learning Accelerator от Nvidia.

Как мы видим, ESP может служить платформой для интеграции сторонних IP-блоков, который может быть размещен на любом из тайлов ESP платформы.

Судя по домашней странице проекта, вся система спроектирована при помощи языка конструирования аппаратуры Chisel и High-Level Synthesis инструментов.

Исходники на HDL, доступные в репозитории проекта, либо относятся к сторонним IP-ядрам/ускорителям, либо созданы с использованием инструментов SoCGen и SocketGen.

Ссылки на проект ESP:

1) github репозиторий

2) сайт проекта

3) документация и туториалы

4) коллекция научных публикаций по тематике проекта ESP

p.s. если кто-то поймет что за Night Vision в правом нижнем углу флурплана чипа - отпишите в комментарии🤔

ESP - это открытая платформа для проектирования и создания гетерогенных System on a chip c возможностью прототипирования системы на FPGA. В будущем планируется также поддержка ASIC design flow.

ESP предоставляет гибкую tile-based архитектуру, построенную на multi-plane network-on-chip

Обзор проекта представлен авторами в статье Agile SoC Development with Open ESP.

В проекте вы найдете знакомые многим RISC-V энтузиастам названия открытых процессорных IP: Ariane (CVA6), ibex, LEON3 (на базе SPARC V8 32-bits ISA). Но самые внимательные увидят на изображении floorplan'а чипа в заголовке поста NVDLA —opensource Deep Learning Accelerator от Nvidia.

Как мы видим, ESP может служить платформой для интеграции сторонних IP-блоков, который может быть размещен на любом из тайлов ESP платформы.

Судя по домашней странице проекта, вся система спроектирована при помощи языка конструирования аппаратуры Chisel и High-Level Synthesis инструментов.

Исходники на HDL, доступные в репозитории проекта, либо относятся к сторонним IP-ядрам/ускорителям, либо созданы с использованием инструментов SoCGen и SocketGen.

Ссылки на проект ESP:

1) github репозиторий

2) сайт проекта

3) документация и туториалы

4) коллекция научных публикаций по тематике проекта ESP

p.s. если кто-то поймет что за Night Vision в правом нижнем углу флурплана чипа - отпишите в комментарии

Please open Telegram to view this post

VIEW IN TELEGRAM