tgoop.com/cpu_design/162

Last Update:

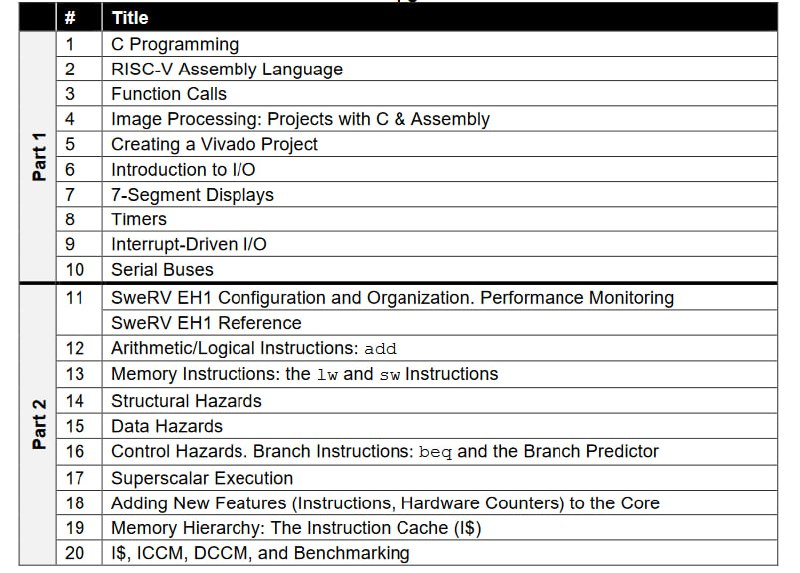

Вышло обновление лучшего курса по работе с RISC-V ядром - RVfpga 3.0

Из новинок в курсе можно выделить основные изменения:

1) Поддержка Catapult SDK от Imagination (только VeeR EL2), автор канала настоятельно рекомендует продолжать пользоваться PlatformIO для получения большего набора компетенций и навыков.

2) Была добавлена предварительно настроенная виртуальная машина на базе Ubuntu с установленным всем необходимым программным обеспечением. Это существенно облегчает начало работы с учебным материалом.

3) Добавлена поддержка ядра VeeR EL2, меньшего по размеру ядра в сравнении с оригинальным ядром курса - VeeR EH1. Данное изменение позволит адаптировать под курс больше отладочных плат с менее мощными и дешевыми FPGA на борту.

4) Добавлены инструменты симуляции RVfpga-ViDBo and RVfpga-Pipeline. Их исходники можно найти в курсе и изучить возможность адаптации простейших тулов ко-симуляции для ваших личных задач и нужд.

Для того чтобы получить доступ к курсу необходимо заполнить специальную форму академического доступа. В течении 1-3 рабочих дней вам должны предоставить ссылку для скачивания материалов.

BY Записки CPU designer'a

Share with your friend now:

tgoop.com/cpu_design/162