tgoop.com/cpu_design/86

Last Update:

Berkeley Out-of-Order RISC-V Processor, Vector, Chisel, Джим Кэллер

Всем привет. Наконец-то появилось свободное время и желание что-то написать в канал.

За месяц с лишним в мире RISC-V произошло много интересных релизов поэтому самое время о них рассказать.

🐌🐌🐌

Успели и SiFive выпустить чип на фабе Intel’a, вышел очередной первый в мире ноутбук на RISC-V чипе, обновились требования RISC-V Profiles, появилась обязательное требование поддержки минимального наборе инструкций половинной точности fp-арифметики Zvfhmin Proporsal в ветке Vector Extension.

Но обо всем по порядку.

Сегодня хочу написать про крутое пополнение в мире процессорных opensource IP. Компания Tenstorrent у которой CTO & President Джим Кэллер представила интересный проект: RISC-V Ocelot.

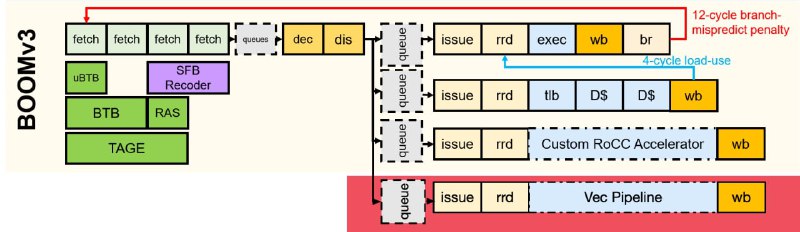

Что такое RISC-V Ocelot? В основе лежит ядро BOOM, одно из первых ядер с полноценной поддержкой Out-of-order. Ядро написано на языке Chisel, в университете Berkeley.

В качестве модернизации процессора, были обновлены существующие исходники BOOM и отдельным in-order конвейером реализован VPU. В проекте представлена краткая микроархитектурная документация. Обратите внимание, что часть векторных инструкций, а именно конфигурационные векторные инструкции, разработчики решили имплементировать на базе существующих скалярных блоков, а не переносить всю логику обработки векторных инструкций непосредственно в VPU pipeline.

Чем интересен этот проект?

• Почти полноценная реализация Vector Extension ( нет поддержки исключений для векторных инструкций, векторного деления, и.т.д., подробности тут)

• Проект написан на Chisel hardware construction language

• Проект собирается и тестируется при помощи Chipyard Framework (сейчас разбираюсь как собрать Ocelot для оценки HW utilization, запуска простых тестов)

p.s. если у кого есть опыт работы с Chipyard отпишитесь в комментариях🙃

BY Записки CPU designer'a

Share with your friend now:

tgoop.com/cpu_design/86