tgoop.com/cpu_design/166

Last Update:

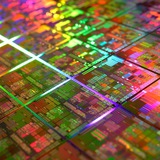

Бесплатная конференция по маршруту верификации и прототипирования Систем на Кристалле от инженеров Yadro

Делюсь с вами ссылкой на открытый хардверный митап.

Со списком докладов вы можете ознакомиться на сайте митапа.

Особое внимание хочется обратить на доклад Анатолия Лернера "Имплементация больших дизайнов на FPGA-кластерах". Прототипирование IP-блоков на реальном оборудовании является актуальной задачей любой компании, которая занимается дизайном в сфере микроэлектроники. Размещение целевого дизайна на FPGA-плате превращается из рутинной задачи в сложную инженерную проблему, когда дизайн распределяется по 2, 3 или даже 8 кристаллам FPGA. Это влечет за собой необходимость в разработке методов распределения частей дизайна по различным физическим чипам, создании систем обмена данными между отладочными платами и чипами, а иногда и разработке единой материнской платы для всего кластера.

Представители большой тройки EDA так же представляют услуги по прототипированию дизайна на FPGA-кластерах.

Например один из продуктов ведущего разработчика EDA, Synospsys - это продажа специальной платформы прототипирования HAPS.

Siemens, не так давно приобрела компанию proFPGA, которая специализируется на проектировании FPGA-кластеров для задач прототипирования.

Интересно, как подошли к решению этой задачи инженеры из команды Yadro.

Для участия в офлайн или онлайн части конференции нужно пройти предварительную регистрацию на сайте ивента.

BY Записки CPU designer'a

Share with your friend now:

tgoop.com/cpu_design/166