tgoop.com/cpu_design/98

Last Update:

Сегодня начинаем новую рубрику - best practice, по мнению автора канала конечно же

На повестке дня: Set membership (inside) operator

Открыл для себя новый оператор в SystemVerilog для задач в синтезируемом подмножестве языка.

SystemVerilog привнес интересные нововведения в языке, которые должны были упростить жизнь RTL-инженерам. Например interface или modport, но EDA тулы до сих пор не могут выдать стабильные результаты синтеза SystemVerilog кода, при использовании новых фич языка.

Спасибо хотя бы за enum и package. Теперь наследовать параметры, и описывать fsm стало на порядок проще и удобнее.

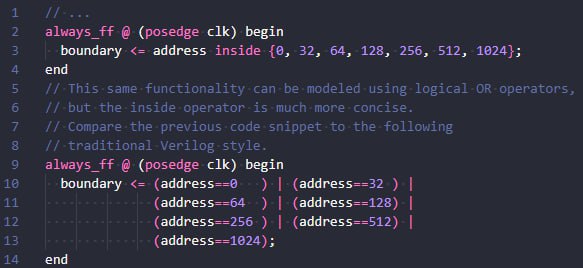

Что же делает оператор inside?

Оператор возвращает 1'b1 если сравниваемое выражение [слева от ключевого слова inside] совпадает с любым из выражений в наборе {}, в остальных случаях 1'b0 (синтаксис смотри на скриншоте).

Как и где применять?

▫️построение зависимостей внутри FSM

▫️поиск битовой подстроки в битовом векторе:

always_comb begin▫️поиск элемента в массиве хранимых регистров

flag = data_in inside {8'b??0011??};

end // true if the middle bits of data match 4'b0011

always_comb begin▫️пример из моего текущего проекта - при помощи

prime_val = data_in inside {data_set_array};

end // true if data matches a value inside the data_set_array array

inside определяю тип команды для FMA блока: FMADD,FMSUB,FNMADD, и.т.д - в зависимости от команды понимаю нужно ли мне изменять знак одного из операндов или нет. Очень удобная замена ==, | операторов получилась.Протестировал оператор в Synopsys 2022.1, Vivado 2020.1, Siemens Oasys-RTL 2022.1.R1, Cadence Genus 21.1. Все эти тулы поддерживают стандарт SystemVerilog-2012 (IEEE Standard 1800-2012), не уверен что тулы, которые поддерживают стандарты 2009-го или 2005-го года корректно работают с

inside

#bestpractice