tgoop.com/cpu_design/81

Last Update:

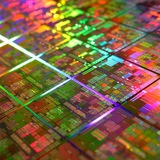

OpenSource SoC на базе RISC-V с eFGPA QuickLogic

Кажется это первое ядро с открытым исходным кодом, где имплементирована eFPGA.

Наличие eFPGA позволяет реализовать кастомные решения для ускорения вычислительных операций, проектирования кастомного интерфейса.

Для ускорения арифметических операция на борту eFPGA находятся два блока MAC. Которые могут быть синтезированы в один 32-битный вычислитель, два 16-битных или четыре 8-битных.

На борту eFPGA ≈ 6k LUT(5)s, 4k FFs. По емкости соответствуетco, например, ice40up.

Программируется eFPGA непосредственно через CPU по шине APB.

Построен СнК на базе cv32e40p. Классическое 4-стадийное in-order ядро. Поддерживаемые расширения - RV32IM[F]C

Документацию на проект можно найти - тут

Подробную статью о имплементации eFPGA в SoC можно найти - тут

p.s. спасибо Мише Коробкову, что поделился ссылкой на проект

BY Записки CPU designer'a

Share with your friend now:

tgoop.com/cpu_design/81