Записки CPU designer'a

Делюсь впечатлениями от доклада про поддержку Posit-вычислений в RISC-V процессорах. Расстроило, что для поддержки Posit инструкций просто смапили наборы F/D. То есть программа может работать, либо с IEEE-754, либо с Posit. Одновременно перегонять плавучку…

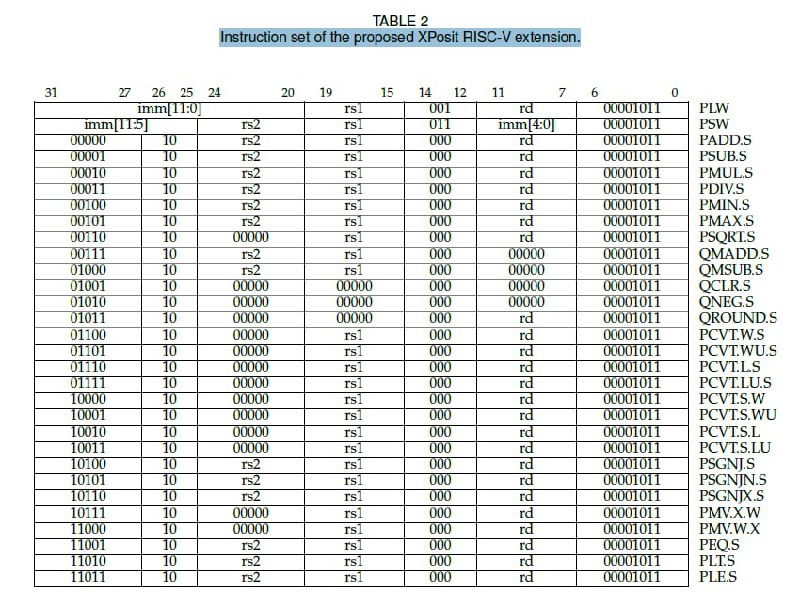

В контексте бесед о Posit и его поддержки на уровне расширения в ISA RISC-V рекомендую почитать эту статью (спасибо Doke за ссылку). Здесь разбирается "proposed XPosit RISC-V extension".

Тема для размышлений:

Напомню, что в Posit только 1 режим округления. Посмотрите на набор инструкций для поддержки расширения F - там 3 бита отведены под поле rm (rounding mode).

Как это можно/нужно обыграть на уровне проектирования Posit-extension?

Тема для размышлений:

Напомню, что в Posit только 1 режим округления. Посмотрите на набор инструкций для поддержки расширения F - там 3 бита отведены под поле rm (rounding mode).

Как это можно/нужно обыграть на уровне проектирования Posit-extension?

tgoop.com/cpu_design/50

Create:

Last Update:

Last Update:

В контексте бесед о Posit и его поддержки на уровне расширения в ISA RISC-V рекомендую почитать эту статью (спасибо Doke за ссылку). Здесь разбирается "proposed XPosit RISC-V extension".

Тема для размышлений:

Напомню, что в Posit только 1 режим округления. Посмотрите на набор инструкций для поддержки расширения F - там 3 бита отведены под поле rm (rounding mode).

Как это можно/нужно обыграть на уровне проектирования Posit-extension?

Тема для размышлений:

Напомню, что в Posit только 1 режим округления. Посмотрите на набор инструкций для поддержки расширения F - там 3 бита отведены под поле rm (rounding mode).

Как это можно/нужно обыграть на уровне проектирования Posit-extension?

BY Записки CPU designer'a

Share with your friend now:

tgoop.com/cpu_design/50