tgoop.com/cpu_design/106

Last Update:

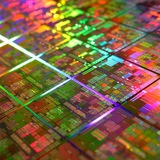

The OpenROAD 7nm Physical Design Contest

Всем привет, сегодня расскажу вам о контексте от OpenROAD.

OpenROAD это открытый маршрут проектирования RTL-to-GDS. От этапа написания Verilog кода, до отправки заветного архива с GDS на фабрику.

Примеры открытых проектов, разработанных при помощи инструментария OpenROAD вы можете найти на сайте efabless в разделе Open MPW.

Например, проект микроконтроллерного ядра. Аналог AtMega328 [аналог по функционалу, но с лучшим перфомансом]. Ядром микроконтроллера выступает opensource IP от Syntacore SCR1.

Контест подразумевает работу не с HDL, а с инструментарием OpenROAD и 7нм [7нм Карл!] учебной библиотекой от ASU. Так что, software инженеры, самое время коллабится с железячниками и вкатываться в контест.

На контесте два основных направления.

Problem A Best Performance. Задача — работая с репозиторием OpenROAD-flow-scripts добиться лучшего перфоманса для целевого дизайна. Критерий лучшего перфоманса "Best fmax with 0 wns".

Problem B Best Possible Runtime. Репозиторий тот же, но теперь нужно добиться наилучшего Runtime без значительных отклонений по площади и частоте для целевого дизайна. То есть улучшая показатель рантайма ваши изменения в конфигурационных скриптах не должны превратить дизайн процессора в счетчик или в огромный последовательный сумматор. "For the given machine setup, minimize runtime for best area and performance."

В качестве целевых дизайнов предлагается 3 ядра на базе RISC-V:

1) RISC-V32i

2) ibex

3) swerv_wrapper

Награда за победу в одной из категорий 500 долларов 💰

Процесс регистрации в контесте, сроки, системные требования для установки OpenROAD, дополнительные призовые категории, смотри на сайте соревнования. Так же на сайте найдешь канал в gitter, slack, e-mail, куда можно задать любые интересующие тебя вопросы. 🤓

GLHF!